울산과학기술원 연구진이 고성능 첨단 반도체 개발에 필수적인 전력 관리 소자를 초소형화하면서 성능까지 크게 향상시킨 신기술을 선보였다. 급변하는 전류 환경에서 안정적인 전압을 유지하는 데 중요한 역할을 하는 이 반도체는 차세대 AI 반도체와 6세대(6G) 통신 칩 등 차세대 시스템 반도체 분야에서 광범위하게 활용될 수 있을 것으로 보인다.

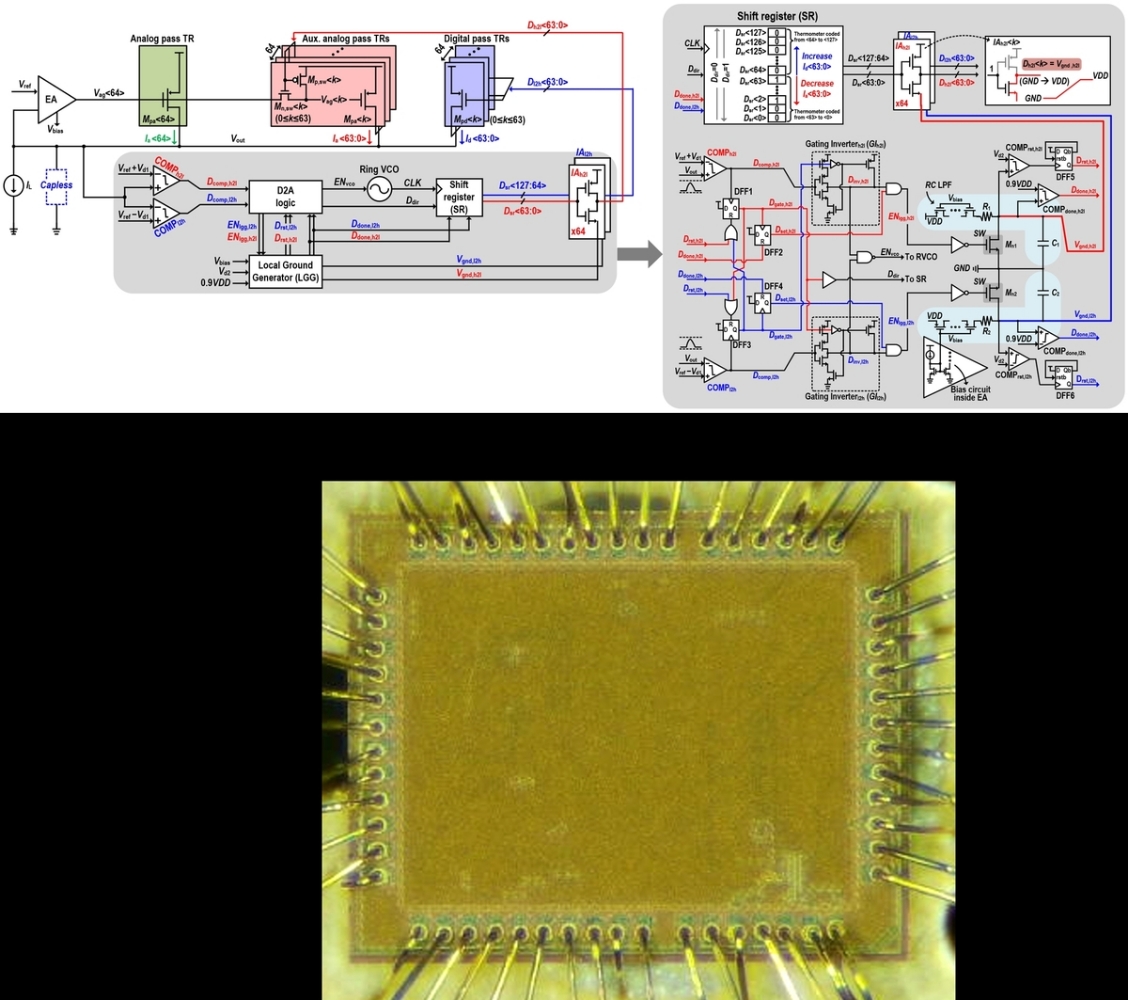

울산과학기술원(UNIST) 전기전자공학과 윤희인 교수 연구팀은 하이브리드 구조의 초소형 전력 관리 반도체인 LDO(Low DropOut Regulator)를 새롭게 개발했다고 9월 29일 밝혔다. LDO는 메인 반도체에 공급되는 전류와 전압을 안정화시키는 보조 반도체 소자다. 이번에 개발된 LDO는 아날로그와 디지털 회로의 장점을 결합한 하이브리드 방식으로, 크기를 줄이면서도 전압 변동을 빠르게 안정화시키고 외부 잡음을 효과적으로 억제하는 성능을 갖추고 있다.

스마트폰을 예로 들면, 게임 앱처럼 전력 소모가 큰 기능을 갑자기 실행하거나 종료할 경우, 내부 회로에서 전류 수요가 급격히 변화해 전압이 들쭉날쭉해질 수 있다. 이러한 전압의 흔들림은 반도체 장치의 오작동을 유발할 수 있기 때문에, 이를 평탄하게 유지하는 부품의 역할이 매우 중요하다. UNIST 연구팀의 신형 LDO는 이런 상황에서 전류가 99밀리암페어(mA)까지 급변하더라도 출력 전압의 변동 폭을 54밀리볼트(mV) 수준으로 억제했고, 불안정한 전압을 667나노초(ns) 만에 정상 상태로 복귀시켰다. 이는 현존 최고 수준의 응답 성능이다.

또한 외부로부터 유입되는 전기적 잡음을 제거하는 능력도 크게 향상됐다. 잡음 억제 성능(PSRR, Power Supply Rejection Ratio)은 -53.7데시벨(dB, 10킬로헤르츠 기준)로 평가됐다. 이는 10킬로헤르츠 주파수에서 들어온 잡음의 약 99.8%를 걸러낸다는 의미로, 고성능 회로 설계에 있어 매우 우수한 수치다. 특히 디지털 회로가 전류 변화가 있을 때만 작동하도록 설계되어 있어 대기 전류(standby power) 소모도 큰 폭으로 줄였다.

윤희인 교수는 “이번 성과는 인공지능 반도체나 초고속 통신 칩처럼 고성능과 고효율이 동시에 요구되는 첨단 시스템온칩(SoC) 개발에서 중요한 기반 기술이 될 수 있다”고 밝혔다. 실제로 이번 연구 성과는 회로 설계 분야의 권위 있는 학술지인 ‘저널 오브 솔리드 스테이트 서킷(Journal of Solid-State Circuits)’에 게재되며 관련 학계에서는 큰 관심을 받고 있다.

이 같은 기술 발전은 차세대 반도체 소자의 고도화뿐 아니라, 스마트폰·자율주행차·AI 서버 등 고성능 전자기기 전반의 전력 효율을 높이고 안정성을 강화하는 데 기여할 수 있을 것으로 기대된다. 특히 시스템 반도체 분야에서 고성능을 요구하는 트렌드가 강화됨에 따라, 초소형·고효율 전력 관리 기술의 수요는 앞으로도 더욱 중요해질 전망이다.

0

0

![[오후 뉴스브리핑] 미국과 이란, 잠정 휴전안 조율 중 外](https://f1.tokenpost.kr/2026/04/whias2y74r.jpg)

![[모닝 뉴스브리핑] 트럼프 대통령, 이란과 심도 있는 협상 중 外](https://f1.tokenpost.kr/2026/04/96ypyo0yto.jpg)

![[토큰명언]](https://f1.tokenpost.kr/2026/04/txms7ae94k.jpg)

![[Episode 12] IXO™2024 참여하고, 2억원 상당 에어드랍 받자!](https://f1.tokenpost.kr/2024/03/bk2tc5rpf6.png)

![[Episode 11] 코인이지(CoinEasy) 에어드랍](https://f1.tokenpost.kr/2024/02/g0nu4cmps6.png)

![[Episode 8] Alaya 커뮤니티 입장하고, $AGT 받자!](https://f1.tokenpost.kr/2023/10/0evqvn0brd.png)

![[Episode 6] 아트테크 하고, 에어드랍 받자!](https://f1.tokenpost.kr/2023/08/3b7hm5n6wf.jpg)

![[토큰포스트] 기사 퀴즈 567회차](https://f1.tokenpost.kr/2026/04/imyrxjn9es.jpg)

![[토큰포스트] 기사 퀴즈 566회차](https://f1.tokenpost.kr/2026/04/n9mlws44zz.png)

![[토큰포스트] 기사 퀴즈 565회차](https://f1.tokenpost.kr/2026/03/m43jkd7zqs.jpg)

![[토큰포스트] 기사 퀴즈 564회차](https://f1.tokenpost.kr/2026/03/jv98dr88vq.png)